Considerations for Implementing a Zone-Selective Interlocking Scheme on Medium and Low Voltage Systems

Matt Proctor- GE Grid Automation

2018 - Houston IEEE

## **Zone-Selective Interlocking**

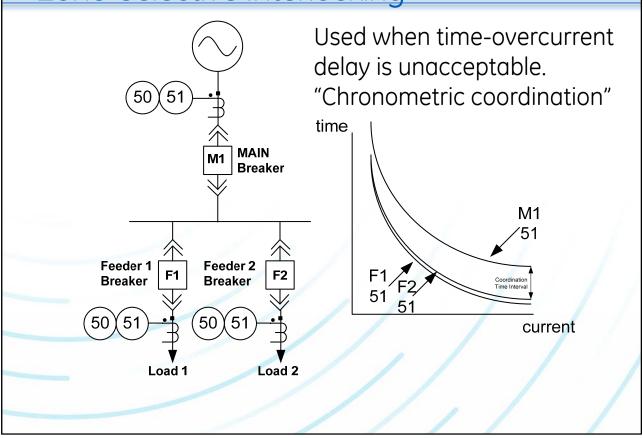

There is an inherent consequence in using coordinated time-overcurrent protection. It can be very slow. ZSI can be applied when time-overcurrent delay is not acceptable.

- Applied to lines or buses.

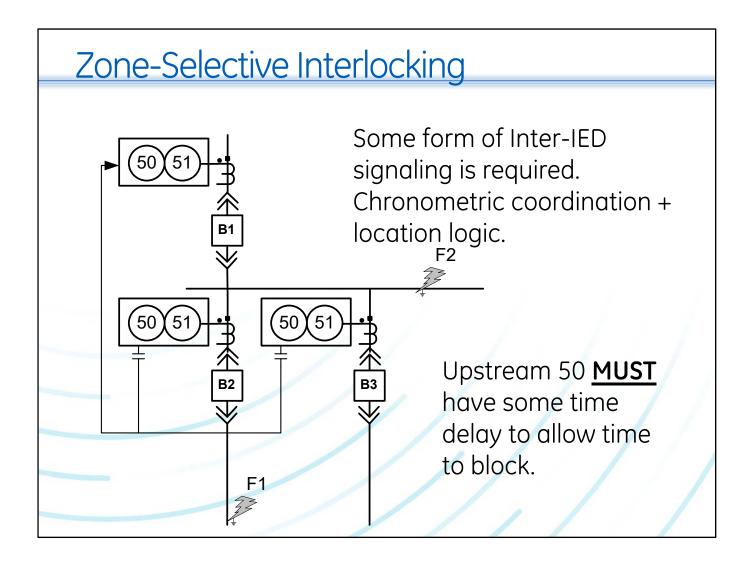

Configure and apply time-overcurrent protection as normal. It still serves as a backup. For fault F1, B2 relay would initiate a blocking signal to prevent the B1 50 from tripping. For fault F2, B1 50 would not be blocked, and it would be allowed to trip fast, without the typical time-coordination delay.

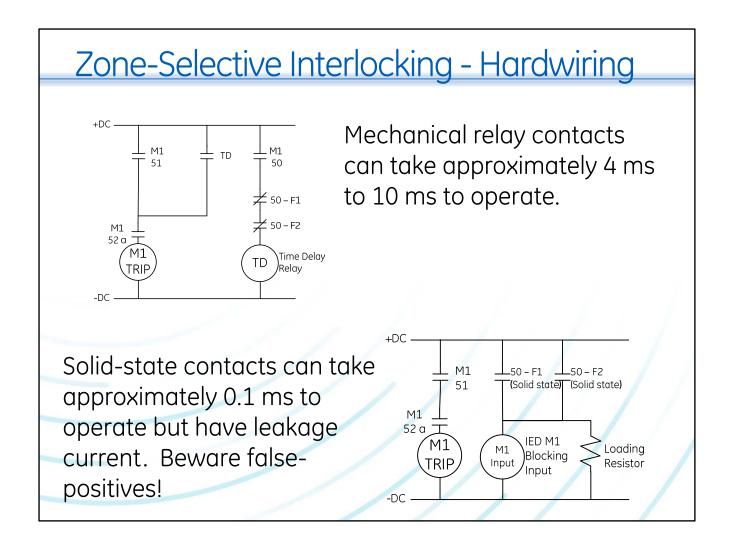

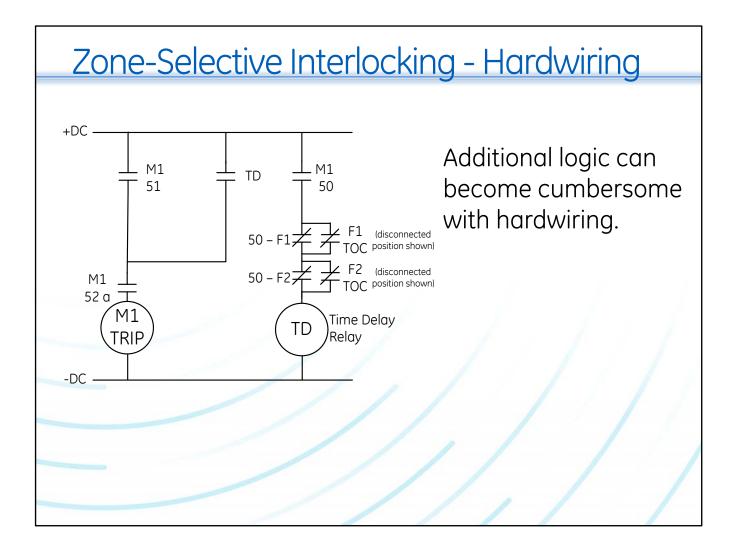

Zone selective schemes did not come into existence because of modern digital relaying. "Location Logic" can be implemented with hardwiring.

Where available, solid state relay contacts can be used to expedite signaling, but beware the adverse effects of the snubber circuitry.

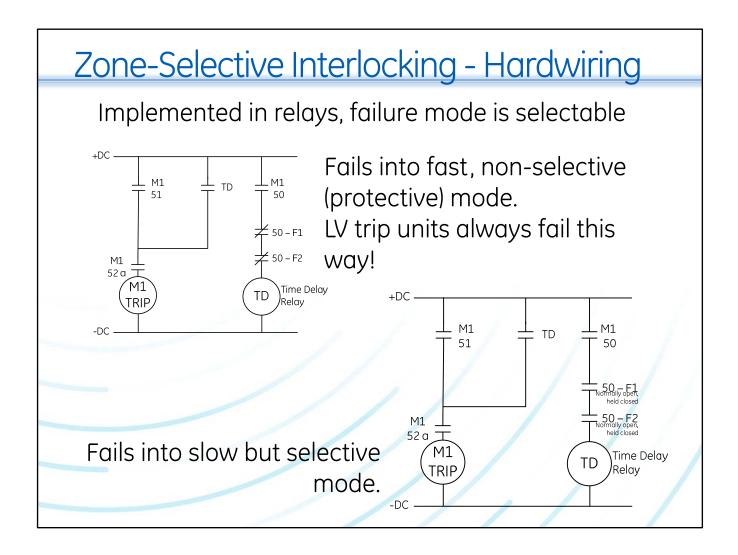

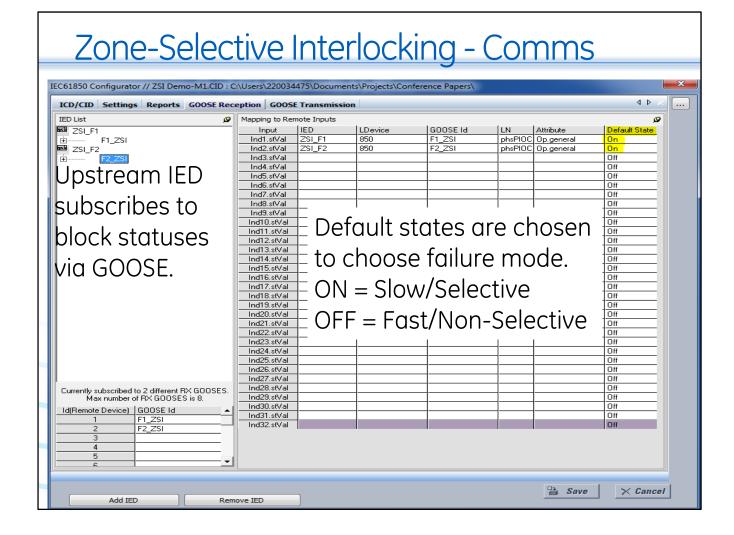

In a hardwired scheme, selection of the failure mode can be done by applying normally open or normally closed contacts.

This hardwiring shows the restraining relays being removed from the circuit when the breaker is racked out of position. You wouldn't want to affect your ZSI when you are pushing test currents through a relay whose breaker is racked out. Notice that wiring could get complicated as buses get larger.

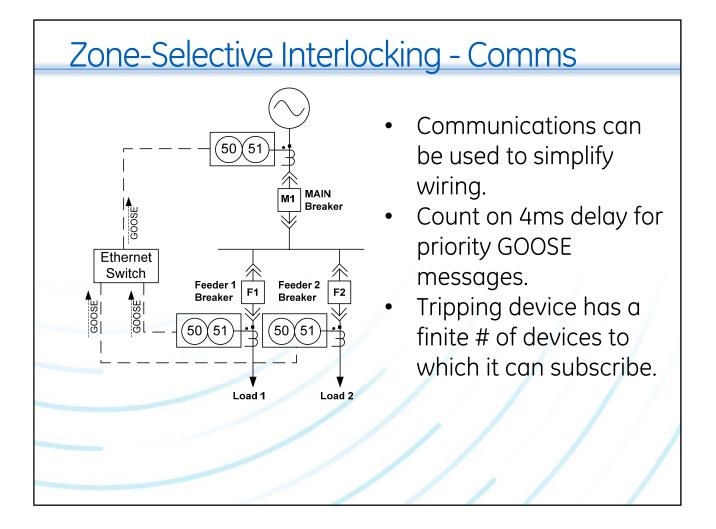

Beware proprietary protocols because of possible timing variance. By 61850 standard, a GOOSE message is transmitted, received and parsed in  $\frac{1}{4}$  of a cycle.

Be aware that complex network architectures could introduce scenarios where unwanted messaging delay can occur.

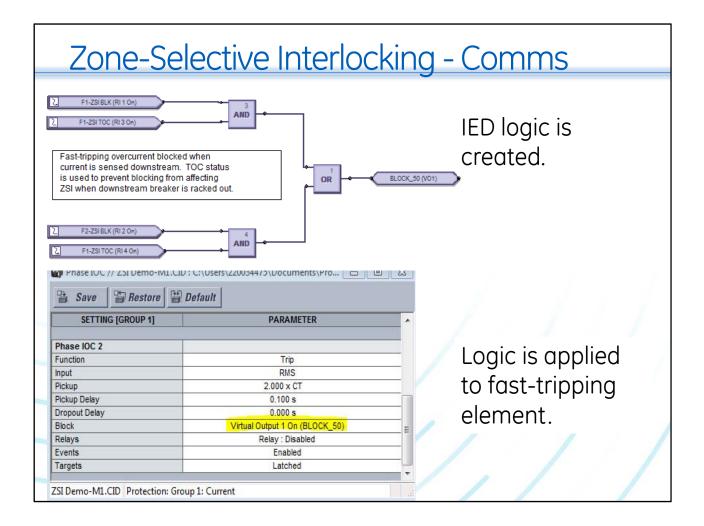

Comms greatly reduces hardwiring complexity and offers greater flexibility to change the scheme's implementation.

It's a good idea to monitor comms with an actionable loss of comms alarm.

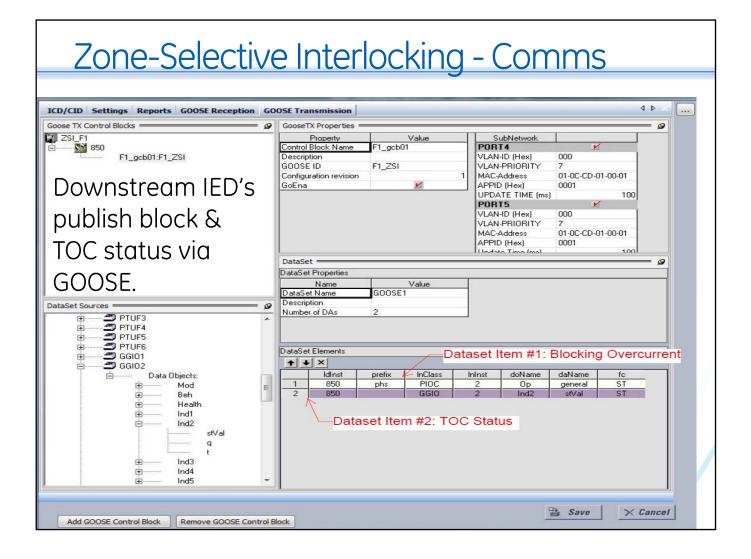

IEC61850 is a multicast messaging system, so several "restraining" relays can be programmed to publish the restraint signal.

Comms can be configured to accomplish the same jobs as the hardwiring scheme.

The IED is configured to default to an ON or OFF state when comms are lost. This is akin to configuring a hardwired scheme with "normally closed" or "normally open" contacts.

This logic is identical to the cumbersome wiring shown on a previous slide.

With comms, the scheme can be changed, or breakers can be added to the logic without having to change any wiring.

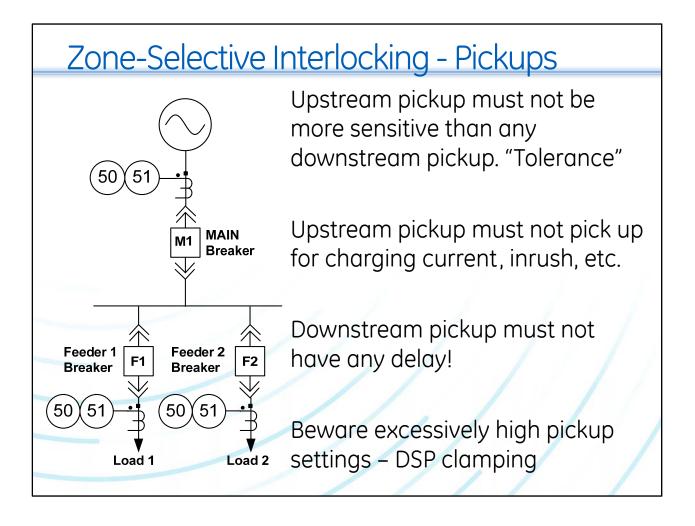

Under no circumstance should the upstream tripping relay detect a feeder fault that is not detected by a blocking relay.

Setting the fast tripping element pickup equal to the blocking element pickup may not always be best. Beware the scenario where CT measurement and relay tolerance yield a more sensitive tripping pickup than blocking pickup. It's best to use identical relays and identical CTs. Using low ratio CT's on feeders (downstream) and higher ratio CT's on mains (upstream) present unique challenges.

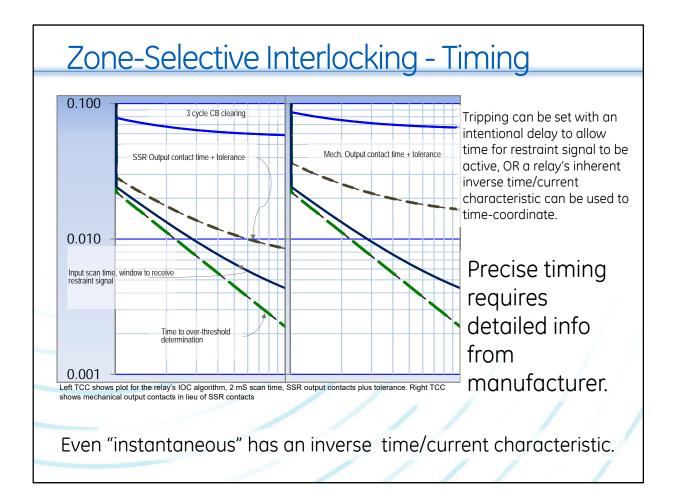

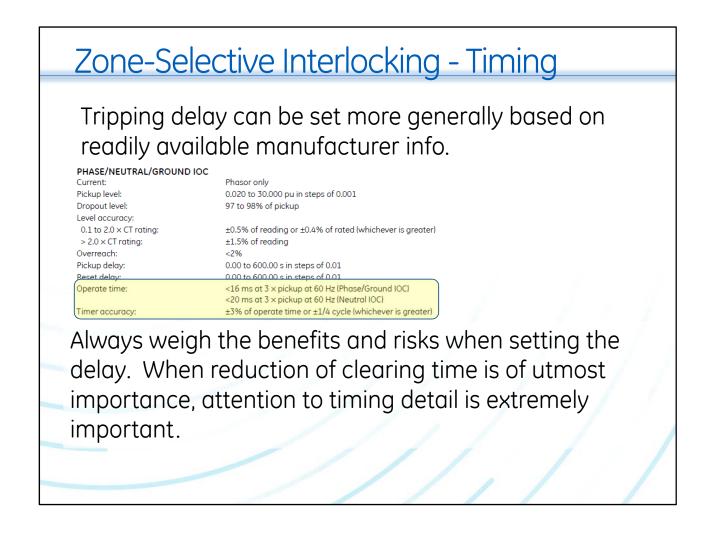

Time must be given for the restraining signal to prevent the fast-tripping relay from operating. This can be done generally, or it can be accomplished more precisely by taking advantage of a device's inherent inverse characteristic.

This precise method is mostly applied in LV applications. Typically, LV trip units are designed and tested to have very precise timing. Those trip units make use of the inherent inverse characteristic in addition to other proprietary methods to ensure proper timing of a ZSI scheme. If precise timing is to be used with IED's on a MV system (or any system for that matter), the reward of marginally quicker clearing time should be weighed against the additional engineering effort and inherent risk of implementing a very precisely timed system.

A more general method of setting the fast-tripping ZSI delay looks at the fastest possible tripping time and the slowest possible blocking time. Then, signaling delay is added. For example, a tripping relay can pickup in 2 ms AT BEST (not typical). A blocking relay might have a published slowest-operating time (assuming all other conditions are within normal operating parameters: no CT saturation, etc) of 20 ms. Factoring a communications time of  $\frac{1}{4}$  cycle, the minimum ZSI trip delay can be assumed to be 20 - 2 + 0.25 = 18.25 ms. Generally, it is a good idea to add additional time to this minimum calculation in order to add extra security to the system. Try not to add too much time so that the Arc Flash PPE Hazard Category is increased.

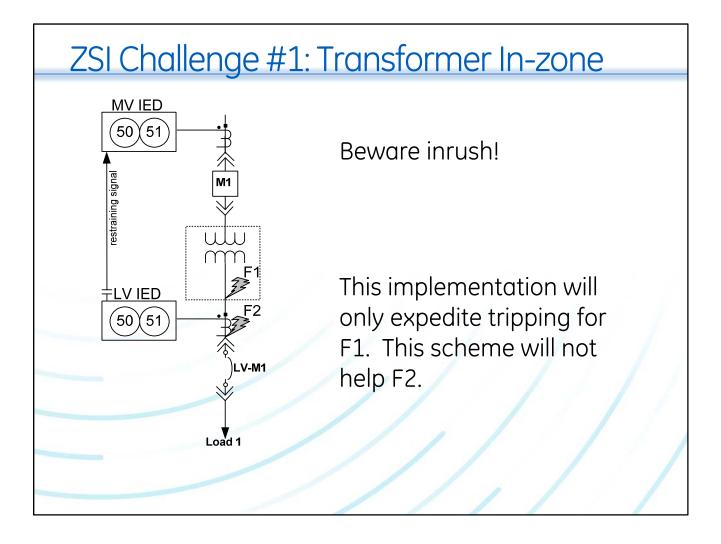

This is a commonly requested/discussed application because at first glance it potentially offers a solution to arc flash concerns without the hassle of installing CT cabling between switchgear for transformer differential. ZSI across a transformer is not recommended, especially for the purpose of arc flash reduction.

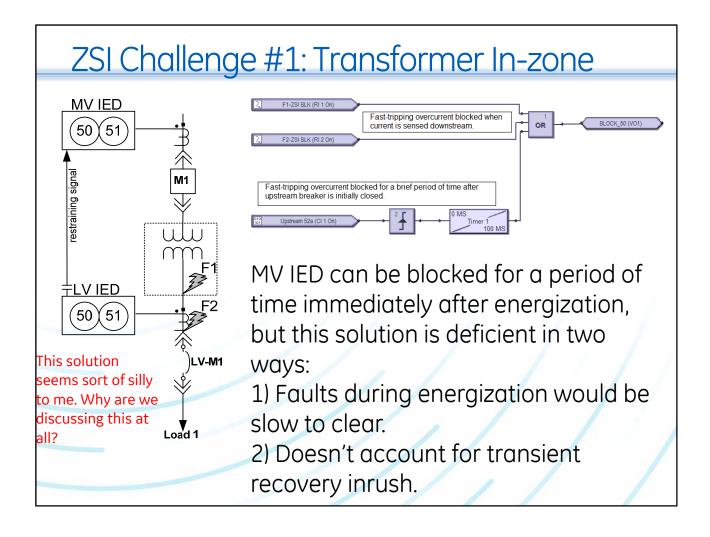

Q: But can't we just block the ZSI for a brief duration after we energize the transformer? Won't that address the inrush problem?

A: No. Inrush does not occur only on initial energization. You are susceptible to a nuisance-trip when supply voltage dips and the transformer incurs recovery inrush. Besides, your protection would be useless during a critical event, initial energization of the switchgear.

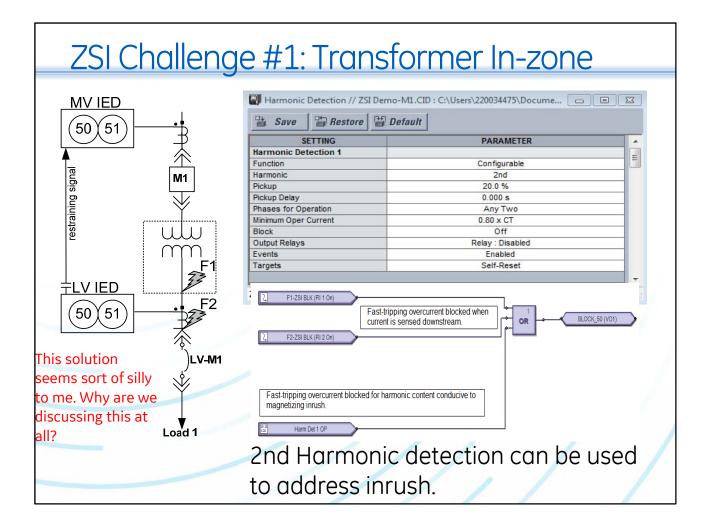

Q: Can we use 2<sup>nd</sup> harmonic blocking to prevent tripping on inrush? After all, this is how we avoid tripping for inrush in an 87T application.

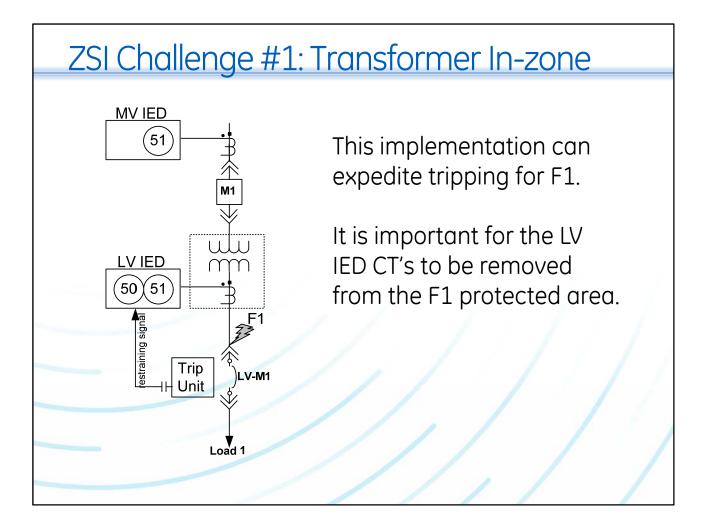

A: Maybe. The concerns with this approach are: 1) That an arcing fault MAY have a significant enough 2<sup>nd</sup> harmonic to initiate a false-block. (PCIC 2018 Paper Pending). and 2) the LV feeder breakers would need to be used as blocking devices, not the main. The Main LV trip unit does not address the problem at F2.

CT placement is key. CT's should be placed away from the incoming stabs to ensure that the arcing fault current is detected.

A tripping signal needs to be sent to the M1 breaker.

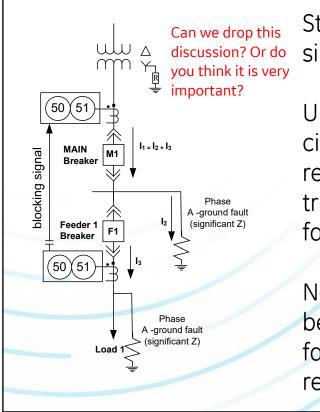

## ZSI Challenge #2: Simultaneous Faults

Stress of 1 fault can cause a simultaneous fault.

Under very specific circumstances, the blocking relay would prevent the tripping relay from operating fast.

Normally, fault current would be re-directed into upstream fault so block would be removed.

The effectiveness of a ZSI has been challenged on the basis that the electrical and mechanical stress from one out-of-zone fault could cause a simultaneous in-zone fault. In such a scenario, the blocking relay would improperly prevent the in-zone fault from being cleared quickly. In reality, this is an extremely unlikely scenario. For this to occur, the fault impedance in the in-zone fault would have to be significant enough to allow fault current to be divided between the two faults in a sufficient enough magnitude to allow arcing. In reality, this is so improbable on industrial MV systems, that it is barely worthy of discussion in regards to arc flash concerns.

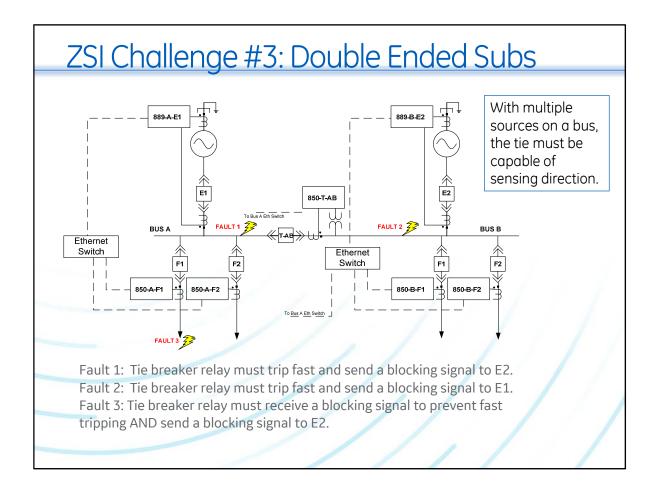

This example demonstrates the need for the TIE relay to be directional. Depending on which Bus the fault occurs, the Tie relay will need to send a blocking signal to the proper Incomer but not both Incomers. VT's will be required for polarization of the overcurrent. For solidly grounded systems, a method of ground overcurrent polarization is required, 3V0 (requires wye VT's) or negative sequence voltage polarization can be applied.

VT Fuse Failure Alarm is recommended. Consider failure mode – Turn off ZSI tripping or default to fast tripping?

Important note: Directional logic can only be truly tested with primary current. Secondary injection is not sufficient.

## Conclusions

- ZSI is a longstanding technology that can be used to expedite otherwise slow time-overcurrent protection.

- The scheme can be implemented in many different ways. Consider the failure mode of the scheme.

- Transformer inrush & substations with multiple sources offer challenges to ZSI implementation.

- Choose your ZSI timing carefully.

Thank You Questions?